# Comparative Performance Analysis of XOR-XNOR Function Based High-Speed CMOS Full Adder Circuits

Bhavani Prasad Y., Harish Babu N., Ramana Reddy K.V., Dhanabal R Sense School

VIT University Vellore Tamilnadu

bhavaniprasad.ece@gmail.com, harishharsha72@gmail.com, ramanareddy428@gmail.com, rdhanabal@gmail.com

Abstract— This CMOS Design, Complimentary Pass Transistor Logic Design and papers presents the realization of full adder designs using Complimentary XOR-XNOR Design in a single unit. The main motive of this paper is to determine the comparative study of power, delay, power delay product(PDP) of different Full adder designs using CMOS Logic Styles. Simulations results clearly determines that XOR-XNOR type Full adder Design is better compared to Complimentary CMOS style and Pass Transistor Design with respect to power, delay. Power Delay Product Comparison. The power delay product is also important parameter to determines the performance of the design. The XOR-XNOR implementation provides better performance and requires less number of transistors compared to other full adder designs. The implementation of design using GPDK 180nm with supply voltage of 1.8 V in Cadence Virtuoso Schematic Composer and simulations done by using Spectre Environment.

Key Words — XOR, Full adders, XNOR, PTL, XOR-XNOR.

# I. INTRODUCTION

Power consumption and delay are two important considerations for VLSI system designer engineers. Our prime motive is to reduce the power and to get less delay that is nothing but the high speed for any design. Adder is one of the fundamental block present in arithmetic logic unit (ALU), floating point unit .In present arena we need fast arithmetic computation cells like adder and multipliers in the very large scale integration (VLSI) designs. The XOR/XNOR is the basic building block in many circuits like Arithmetic circuits.

Compressors, Comparators, Phase detectors, Code converters, Multipliers, Parity Checkers, Error-detecting and Error-correcting codes. Moreover, adders are very important components in some other applications such as microprocessor and digital signal processing (DSP) architectures. Digital signal processors and Microprocessors mainly rely on highly efficient implementations of generic floating point units and arithmetic logic units(ALU).

Full Adder is one of the core element in many of the complex arithmetic logic circuits like multiplication, division, addition. To perform any arithmetic operation, mainly even a small circuit can consume very low power and also it may even take a long time to complete that operation. There are some standard implementations.

Some different logic styles have been used in the past times for design of the full-adder cells[5]-[19] and those techniques are used in this paper. Although they are used for producing similar function and the way of producing transistor count and intermediate nodes are varied. Different logic styles have different advantages such as the size, power dissipation, speed and the wiring complexity of the circuit. Different logic styles have different performance aspects. The size of the circuit depends on the number of transistors and their sizes and also on wiring complexity of the circuit. In order to get switching point to half of VDD proper sizing should have to be done [1]-[4].

#### II. BACKGROUND

Power is the main criteria in all the electronic design equipments. So that's why the designers are trying to minimize the power consumption when designing the task. In CMOS circuits mostly the energy consumed is because of switching activity. Thus the number of nodes in the circuit, energy per every node and also the total number of transaction operations per second, all these factors led to the power consumption. Power dissipation is based on the node capacitances of gate, threshold switching activity and circuit size.

There are four reasons for the power dissipation: dynamic power due to the charging and discharging of capacitance in the circuit because of switching transactions and leakage current is because of reverse bias condition in diode structures, sub threshold leakage, short-circuit current also leads to certain power dissipation occurred due to rise and fall times.

These three are the major components of power dissipation in (CMOS) circuits:

- 1. Dynamic Power: Power consumed by the circuit node capacitance because of transistor switching.

- Short Circuit Power: Power consumed because of current flowing from VDD to ground during switching of the transistor.

- 3. Static Power: Power because of leakage and static currents

The increase in demand for low power and low voltage VLSI circuits can be investigated different levels of design, such as the architectural, circuit, layout and the process technology. At the device level, reduction in supply voltage and reduction in the threshold voltage to reduce the power consumption, where as in layout use of short channel transistors, poly and diffusion areas, shorter metal lines for connecting two various devices. It reduces capacitances in circuit and device level.

On an architectural level, CAD algorithms are required for fewer number of gates which reduces the overall power consumption. All these techniques employed most of the times reduce power increase of delay[1]-[5].

## A. CMOS Full Adder(C-CMOS)

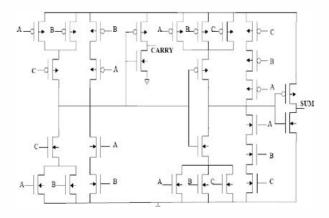

The CMOS full adder(C\_CMOS) is one of the basic full adder circuit shown in below fig.1(a)

Fig. 1(a) complimentary C-CMOS Full Adder Cell[3].

The equation for C-CMOS is given as below

$$Sum = Carry'.(A+B+C) + (A.B.C)$$

$$Sum = ABC + AB'C' + A'BC' + A'B'C \&$$

From the equation we have drawn the pull up and pull down networks and from that we have generated the sum and carry outputs. The advantages of the complimentary CMOS logic circuit are stability and layout regularity at lower voltages due to smaller number of interconnecting wires and complementary pairs of transistors. The C\_CMOS have some robustness against transistor sizing and voltage scaling which can have reliable operation at very low voltages with different transistor sizes.

The second adder is complementary pass transistor logic (CPL) uses 32 transistors with swing restoration. Most CPL gates can have an complexity in interconnection at the layout level with the increase in power and delay. For low power applications Pass Transistor Logic (PTL) is best suitable technique and explanation was given in .The advantage of Pass Transistor Logic (PTL) is that either PMOS or NMOS is enough to implement a complete design [6]-[8] and so number of transistors gets decreased and also smaller input loads, especially for NMOS type of networks and also by this PTL we can eliminate short circuit energy dissipation.

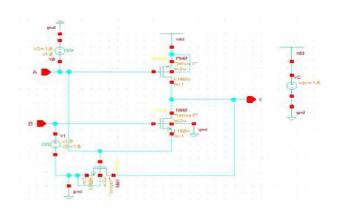

#### B. 3TEXOR

Whenever the input B is of logic 1 or logic 0, then the inverter functions like a normal CMOS inverter. And the output Y is the inverter of input A. Whenever the input B is at logic 0, the

CMOS inverters output is at high impedance(z). However transistor N3 is in on condition and the output Y gets the same value as input A.

whenever A equals to 1 and B equals to 0, voltage reduction happens because of threshold voltage drop occurring across the transistor N3 and also the output Y's performance gets deteriorated when compared to the input value. Degradation can be reduced by increasing the W/L ratio of the transistor N3.

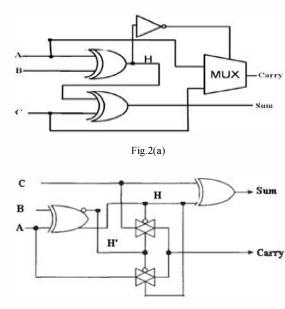

Fig.2(a) 3T EXOR Cell

#### C. 8TADDER USING EXOR GATE

The 8T adder is implemented using 3T EXOR gates The sum output is obtained by a implementing EXOR of the three inputs in The final sum of the products is obtained using a OR logic of PTLtype[15].

Thus two stage are required to obtain the sum value as output and at most in both the stage delays are to be added. The voltage drop due to the threshold in the transistors M3 and M6 can be reduced by increasing the transistor aspect ratios. The input combinations of all the three inputs have been checked by taking the rise and fall time into considerations.

The 8-T EXOR Full Adder is shown in fig. 2(b)

Fig.2(b) EXOR based Full Adder cell

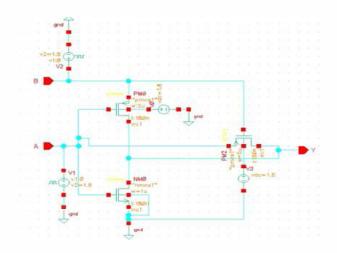

#### D. 3TEXNOR

Similarly like EXOR the EXNOR also can be performed with the transistors to get better performance and optimized the working functionality is given When A=0 and B=0 transistor then p1 becomes on and N1,N2 becomes off so the output gets charged to VDD. A=0 and B=1 circuit shows logic 0 output, because transistor P1 is off and output node gets discharged by transistor N2. A=1 and B=0 then both transistors P1, N1 are on and output is discharged using N1 and N2 transistors. A=B=1, output gives high logic as N1 is on and thus the logic 1 is sent to the output. The 3-T EXNOR based Full Adder is shown in below fig 2(c).

Fig.2(c) 3T EXNOR Cell

## E. 8TEXNOR

It is implemented by two EXNOR gates with one multiplexer block Sum is generated by using two XNOR gates, Carry out is generated by using two transistors multiplexer block. The EXNOR gates with eight transistors has been implemented by using 3T EXNOR gate, The simulation has performed form 3.0V to 1.2V to check the levels of output signal circuit in which it shows desired voltage levels. The 8T EXNOR based Full Adder Cell was shown in below fig .2(d).

Fig.2(d) EXNOR based Full Adder cell

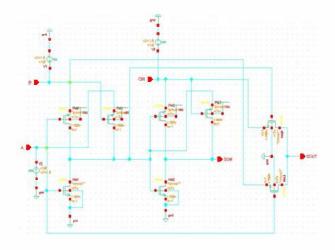

### III. PROPOSED ARCHITECTURE

In this proposed adder we will use one XOR and one XNOR and a multiplexer to generate output sum and carry. The expressions for sum and carry are given in below.

$$Sum = H XOR C = H. C' + H'. C$$

$$Cout = A. H' + C. H$$

$$Sum = (A \oplus B \oplus C) = C' (A \oplus B) + C (A \oplus B)'$$

Where H is (A EXOR B) and H' is compliment of (A EXNOR B).

The proposed adder cell has 16 transistors and is mainly based up on EXOR-EXNOR pass transistor logic and transmission gates.

Fig.2(b)

Fig.3 General Structure of proposed EXOR-EXNOR Adder[13].

In this proposed adder the two transmission gates are used as multiplexer and the sum can be generated by EXOR gates and output carry can be generated by EXOR / EXNOR gates shown in the above figure and output of EXOR gate can be used as the selection line for multiplexer or as the control for the transmission gate which we will get output as the carry. The proposed adder circuit is designed by the combination of the two logic styles in order to get lower power consumption, high speed and good energy efficiency. We know that supply voltage variations will leads to the greater reduction in the power and also in the circuit delay.

#### IV. EXPERIMENTAL RESULTS

All the circuits presented in this paper are designed by using Cadence VIRTUOSO environment by using CMOS process design kit.

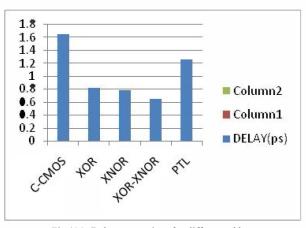

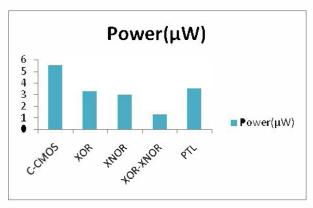

The proposed adder circuit is designed and simulated for different ranges of supply voltages is 1.3V-1.8V. The results of this proposed adder circuit can be compared with the different conventional adder circuit designs. Totally 16 transistors are needed to design the proposed adder circuit. By this we can clearly decide that the proposed circuit can have lower area overhead than the other conventional adder circuits. The delay values of conventional adder circuits and proposed adder circuit are compared and tabulated in below in table. 1 and table. 2. and from the results it is clear that the proposed adder can have very less delay. The proposed circuit can have the lower power values and also lower PDP values as compared to other conventional adder circuits

| Table 1:Simulated | regulte for Full | adder at VDF | =1.3V |

|-------------------|------------------|--------------|-------|

|                   |                  |              |       |

| Type     | Power(μW) |  |

|----------|-----------|--|

| C-CMOS   | 5.521     |  |

| CPTL     | 3.52      |  |

| XOR      | 3.265     |  |

| XNOR     | 2.985     |  |

| XOR-XNOR | 1.295     |  |

Table 2:Simulated results for Full adder at Vdd=1.3V

| Туре     | Delay(ps) | PDP   | # of<br>transistor |  |

|----------|-----------|-------|--------------------|--|

| C-CMOS   | 1.65      | 9.10  | 28                 |  |

| CPTL     | 1.257     | 4.424 | 32                 |  |

| XOR      | 0.825     | 2.64  | 8                  |  |

| XNOR     | 0.785     | 2.345 | 8                  |  |

| XOR-XNOR | 0.653     | 0.832 | 16                 |  |

Fig.4(a): Delay comparison for different adders

Fig 4(b): Power Comparison results for different adders

#### V. CONCLUSION

This paper includes the Implementation of different adder logic styles includes Complimentary CMOS, EXOR- EXNOR, Complementary Pass Transistor Logic and Simulated by using Cadence Environment .The Comparison of power, delay, PDP are tabulated. From the table it is clear that Complimentary CMOS Adder design having more power consumption and delay so more PDP. This paper includes a new adder design of EXOR-EXNOR based adder cell with less power, delay, and power delay product (PDP). Cadence simulations results can show that the new adder design have very less PDP when compared with all other designs. The new full adder design can provide good voltage swing at low supply voltages and provides best performance with respect to all other conventional full adder designs in terms of both speed and power.

#### REFERENCES

- [1] J. M. Rabaey, A. Chandrakasan, B. Nikolic, "Digital Integrated Circuits, A design Perspective," 2nd Prentice Hall, Englewood Cliffs, NJ, 2002.

- [2] J. Uyemura, "CMOS Logic Circuit Design," Kluwer, 1999.

- [3] Sung-Mo Kang, Y. Leblebici, "CMOS Digital Integrated Circuits: Analysis and Design," Tata McGraw Hill, 2003.

- [4] N. Weste, D. Harris, "CMOS VLSI Design," Pearson Wesley, 2005.

- [5] R. Pedram, M. Pedram, Low Power Design Methodologies, Kluwer, Norwell, MA, 1996

- [6] R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass transistor logic," IEEE J. Solid-State Circuit, vol. 32, pp.1079-1090, July 1997.

- [7] U.Ko,P.T.Balsara, W. Lee, "Low Power Design Techniques for High Performance CMOS Adders," IEEE Trans. on VLSI System, vol. 3, pp. 327-333, June 1995.

- [8] D. Radhakrishnan, "Low-voltage low-power CMOS full adder," Proc.Inst. Elect. Engg. Circuits Devices Systems, vol. 148, no. 1, Feb. 2001, pp. 19-24.

- [9] C.H. Chang, J. Gu, M. Zhang, A review of 0.18um full adder performances for tree structure arithmetic circuits, IEEE Trans. Very Large Scale Integration (VLSI) Syst. 13 (6), June 2005.

- [10] A. M. Shams, T. K. Darwish, and M. A. Bayoumi, "Performance Analysis of low-power 1-bit CMOS full adder cells," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 10, no. 1, pp. 20–29, Feb. 2002.

- [11] S. Goel, Ashok kumar, M. A. Bayouni, "Design of Robust, Energy- Efficient Full Adder for Deep-Submicrometer Design Using Hybrid- CMOS Logic Style," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 12, pp. 1309-1321, Dec. 2006.

- [12] Hanho Lee, G. E. Sobelman, "New XOR/XNOR and full adder circuits for low voltage, low power application," Microelectronics Journal vol. 29,pp. 509-517, 1998.

- [13] M. Vesterbacka, "A 14-transistor CMOS full adder with full voltage swing nodes," Proc. IEEE Workshop Signal Processing Systems, Oct 1999, pp. 713-722.

- [14] J. Wang, S. Fang, and W. Feng, "New efficient designs for XOR and XNOR functions on the transistor level," J. Solid State Circuits, vol.29, pp. 780-786, July 1994.

- [15] H.T. Bui, Y. Wang, Y. Jiang, "Design and Analysis of low-power 10-transistor full adders using novel XOR-XNOR gates," IEEE Transactions on Circuits & Systems II, vol. 49, pp. 25-30, Jan. 2002.

- [16] S. Goel, M. E. Elgamel, M. A. Bayouni, Y. Hanafy, "Design Methodologies for high- performance Noisetolerant XOR-XNOR Circuits," IEEE Trans. Circuits and Syst. I, vol. 53, no. 4, pp. 867-868, April 2006.

- [17] K. Navi, O. Kavehei, M. Rouholamini, A. Sahafi, S.Mehrabi, N.Dadkhahi, "Low-Power and High-Performance 1-bit CMOS FullAdder Cell," Journal of Computers, vol. 3, no. 2, pp. 48-54, Feb. 2008

- [18] O. Kavehie, Mostafa Rahimi Azghadi, Keivan Navi and amir Pasha Mirbaha, "Design of Robust and High -Performance 1 Bit CMOS Full Adder for Nanometer Design," IEEE Computer Society Annual Symposium VLSI (ISVLSI), Montpellier Fr., 2008, pp. 10-15.

- [19] Shiv Shankar Mishra, S. Wairya, R.K. Nagaria and S. Tiwari, "New Design Methodologies for High Speed Low Power XOR-XNORCircuits," Journal of World Academy Science, Engineering and Technology (WASET) 09, vol. 55, no. 35, pp. 200-206, July 2009.